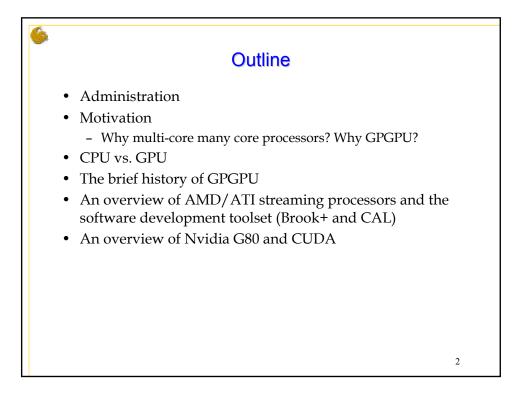

## **Description (Syllabus)**

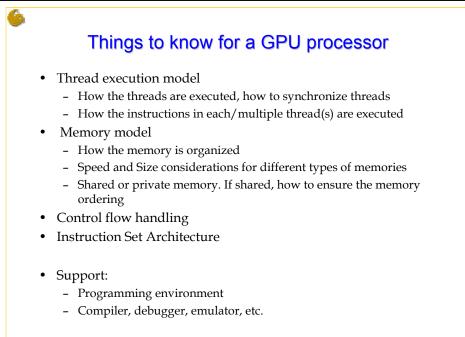

- High performance computing on multi-core / many-core architectures

- Focus:

- Data-level parallelism, thread-level parallelism

- How to express them in various programming models

- Architectural features with high impact on the performance

- Prerequisite

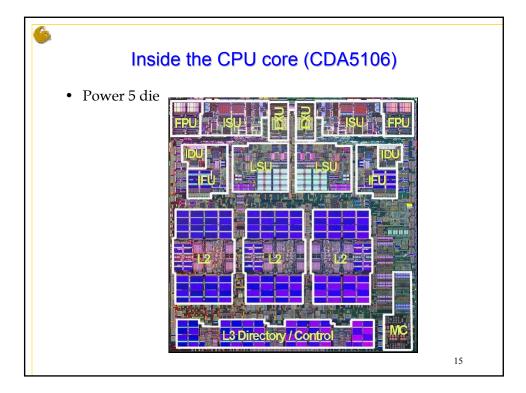

- CDA5106: Advanced Computer Architecture I

- C programming

3

## Who am I

• Assistant Professor at School of EECS, UCF.

- My research area: computer architecture, back-end compiler, embedded systems

- High Performance, Power/Energy Efficient, Fault Tolerant Microarchitectures, Multi-core/many-core architectures (e.g., GPGPU), Architectural support for software debugging, Architectural support for information security

5

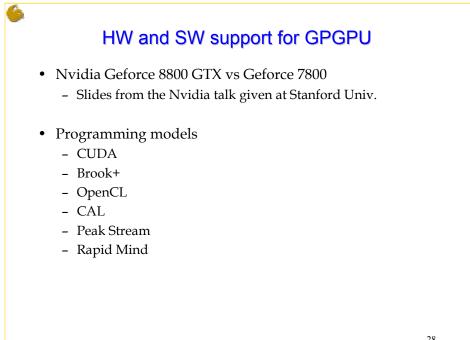

## **Topics** • Introduction to multi-core/many-core architecture Introduction to multi-core/many-core programming • AMD/ATI GPU architectures and the programming model for GPGPU (Brook+ and CAL) (several guest lectures from AMD) • NVidia GPU architectures and the programming model for GPGPU (CUDA) • IBM Cell BE architecture and the programming model for GPGPU • CPU/GPU trade-offs Data-level parallelism and the associated programming patterns • Thread-level parallelism and the associated programming patterns • Future multi-core/many-core architectures Future programming support for multi-core/many-core processors 6

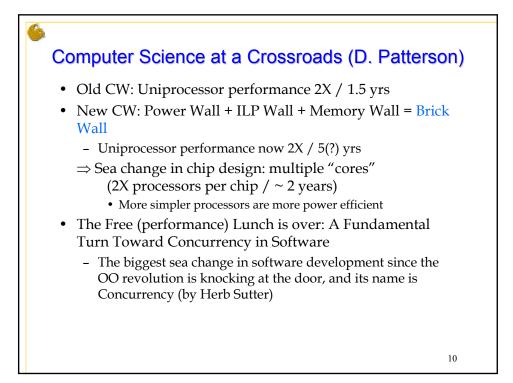

## Problems with Sea Change

- Algorithms, Programming Languages, Compilers, Operating Systems, Architectures, Libraries, ... not ready to supply Thread Level Parallelism or Data Level Parallelism for 1000 CPUs / chip,

- Architectures not ready for 1000 CPUs / chip

- Unlike Instruction Level Parallelism, cannot be solved by just by computer architects and compiler writers alone, but also cannot be solved *without* participation of computer architects

11

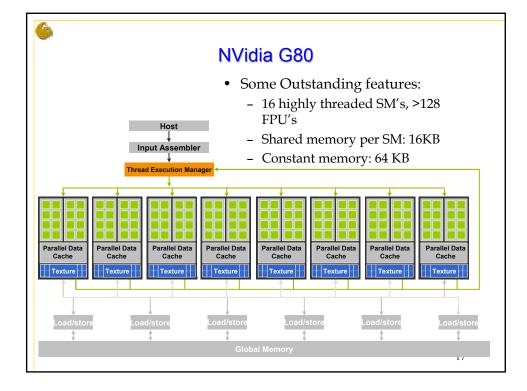

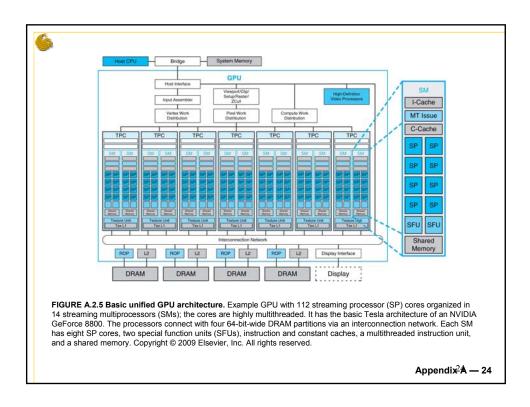

- Modern GPUs run hundreds or thousands threads / chip

- Shifts from Instruction Level Parallelism to Thread Level Parallelism / Data Level Parallelism

- GPGPU is one such example